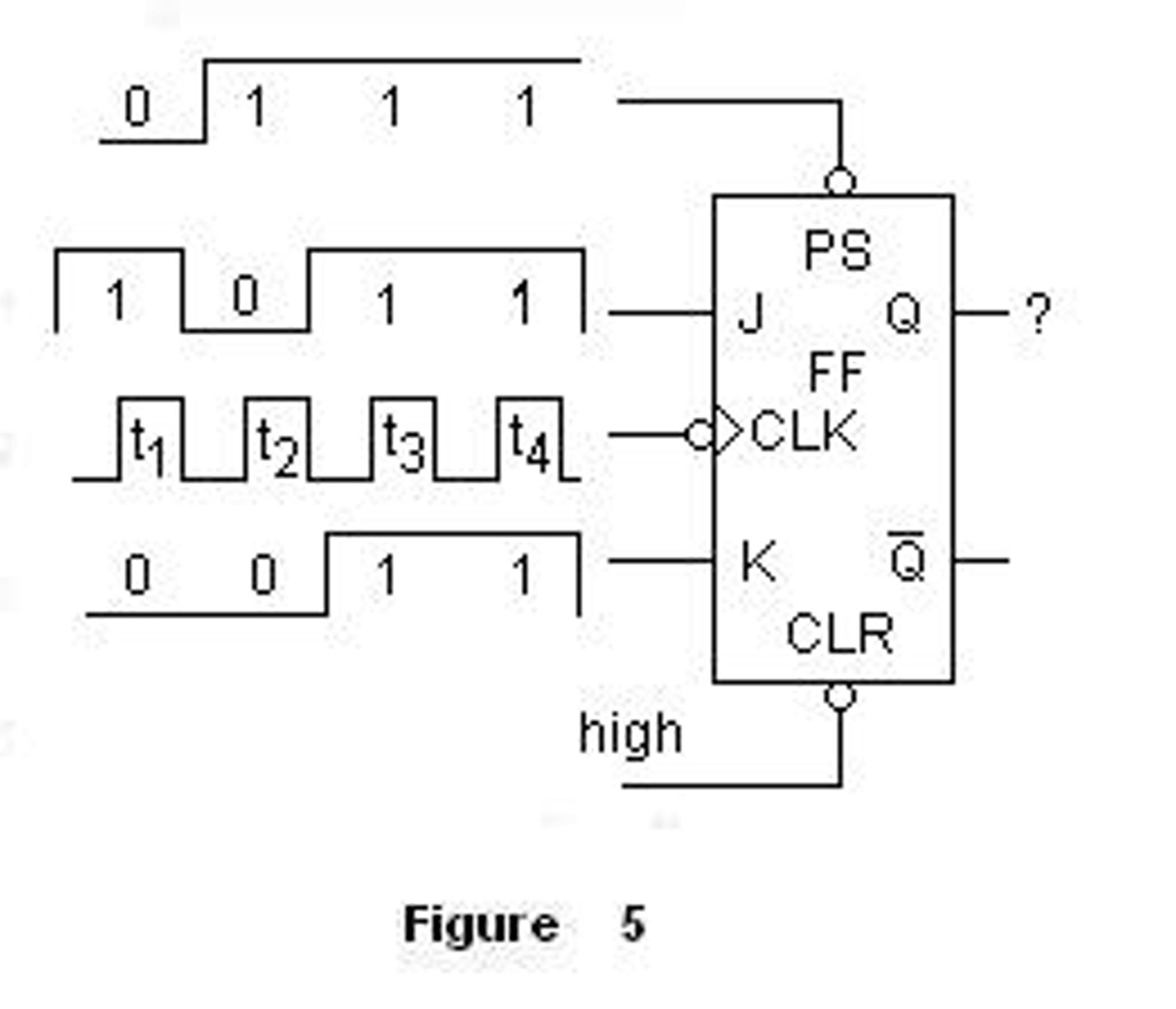

The final output Q then tracks the output of the master section M after a half cycle of the clock. At a half cycle of the clock, on the downward transition, the inverted clock has a positive transition and triggers the slave section. When the clock makes a positive transition the master section is triggered but the slave section is not because its clock is inverted. Another way to look at this circuit is as two J-K flip-flops tied together with the second driven by an inverted clock signal. The Master-Slave JK Flip Flop has two gated SR flip flops used as latches in a way that suppresses the "racing" or "race around" behavior. Since this 4-NAND version of the J-K flip-flop is subject to the " racing" problem, the Master-Slave JK Flip Flop was developed to provide a more stable circuit with the same function. This is an application of the versatile J-K flip-flop. The J & K inputs alone cannot cause a transition, but their values at the time of the PGT determine the output according to the truth table. The "enable" condition does not persist through the entire positive phase of the clock. The positive going transition (PGT) of the clock enables the switching of the output Q. Switching Example: Master-Slave J-K Flip-Flop The next step in making use of the versatile J-K flip-flop is to use four additional NAND gates to create the Master-Slave JK Flip Flop which has two gated SR flip flops used as latches in a way that suppresses the "racing". Modern ICs are so fast that this simple version of the J-K flip-flop is not practical (we put one together in the lab with an available 4-NAND chip and it was very unstable against racing). The timing pulse must be very short because a change in Q before the clock pulse goes off can drive the circuit into an oscillation called " racing". While this implementation of the J-K flip-flop with four NAND gates works in principle, there are problems that arise with the timing. This is what gives the toggling action when J=K=1. Note that the outputs feed back to the enabling NAND gates. HyperPhysics***** Electricity and magnetismĪ simplified version of the versatile J-K flip-flop. This toggle application finds extensive use in binary counters. It can also act as a T flip-flop to accomplish toggling action if J and K are tied together. It can perform the functions of the set/reset flip-flop and has the advantage that there are no ambiguous states. If J and K are both high at the clock edge then the output will toggle from one state to the other. If J and K are both low then no change occurs. The inputs are labeled J and K in honor of the inventor of the device, Jack Kilby. If J and K are different then the output Q takes the value of J at the next clock edge. It has the input-following character of the clocked D flip-flop but has two inputs,traditionally labeled J and K. The J-K flip-flop is the most versatile of the basic flip-flops.

0 kommentar(er)

0 kommentar(er)